[PoliCTF 2012] Write-up GrabBag 200

English version on Big-Daddy's blog

L'épreuve

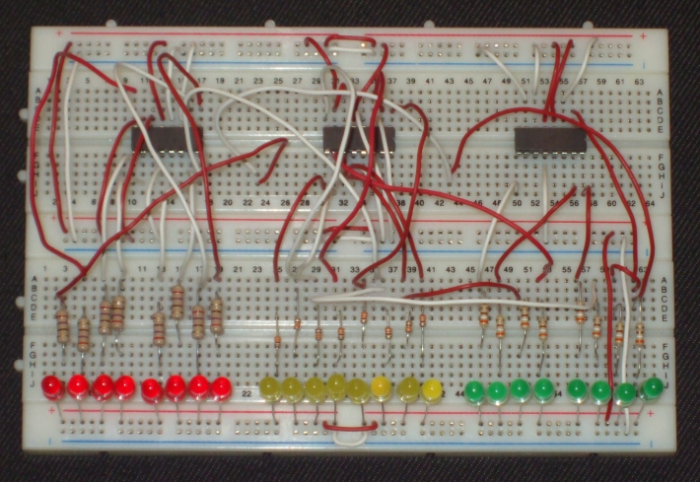

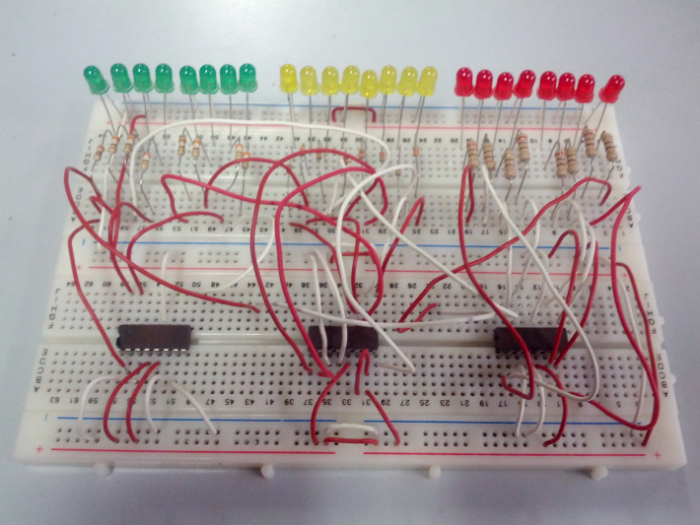

On dispose de 2 photos d'un montage électronique composé de deux plaques d'essai comme on le voit sur la vue générale ci-dessous. Au cours de l'épreuve une troisième photo est donnée par les organisateurs qui permettra de préciser certaines connexions peu visibles sur les photos initiales.

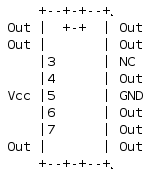

De même les organisateurs fourniront pendant l'épreuve un datasheet (minimal) au format PDF contenant le brochage du circuit utilisé, ce qui fut bien utile pour discriminer la combinaison gagnante.

Le but du jeu est de trouver le code hexadécimal correspondant à l'état des leds lues de droite à gauche.

Résolution

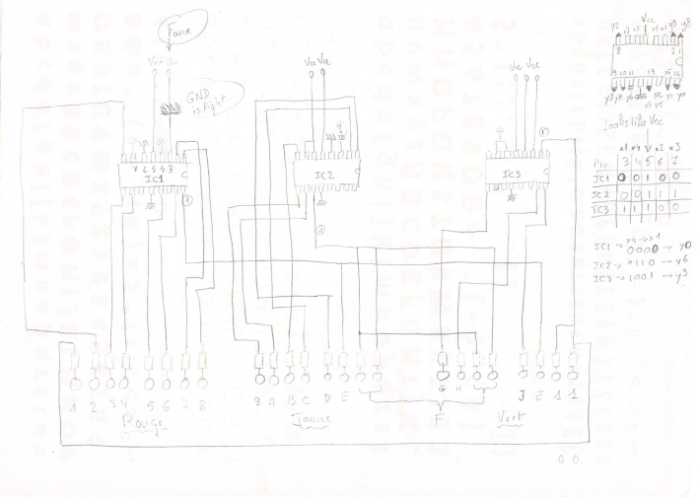

Les 3 circuits intégrés du montage ont leur marquage obfusqué; on ne peut donc pas se baser sur le type de circuit pour deviner ce qui nous attends. On commence donc par établir un schéma de cablâge pour tenter d'y voir plus clair. Le schéma est le suivant:

De ce schéma on peut déduire partiellement le brochage des circuits qui semblent être identiques. On voit que les alimentations sont sur les pattes 5 et 12, ce qui semble exclure qu'il s'agisse de composants "standard" des séries 7400 ou 4000. On compte 9 sorties utilisées et une patte non utilisée soit éventuellement 10 sorties et 4 entrées, ces dernières étant câblées différemment sur chaque CI (pattes 3, 4, 6 et 7 - la patte 5 toujours au Vcc semble être l'alim).

Le brochage supposé du circuit:

Avec donc 10 sorties et 4 entrées il semble que nous soyons face à un décodeur BCD. Il reste donc à trouver le poid de chaque entrée et sortie pour déterminer, en fonction de la combinaison d'entrées, quelle sortie est active sur chaque CI. Et c'est là que le document finalement fourni en cours de compétition par les organisateurs va nous éviter de jouer aux devinettes en nous fournissant cette information. On remarque au passage qu'il ne s'agit pas en effet de composants standard mais de circuits d'origine russe.

le brochage fourni:

On a donc les entrées X1 à X4 du poid faible vers le poid fort et les sorties du décodeur Y0 à Y9. On peut maintenant déterminer précisément quelle sortie de chaque CI est active. Néanmoins il reste une inconnue; les niveaux de tension correspondants à chaque état ne sont pas définis dans le datasheet fourni. On peut donc envisager deux possibilités; toutes les sorties à Vcc sauf la sortie active (logique négative), ou au contraire toutes les sorties à 0 volt sauf la sortie active (logique positive). Sachant qu'il faut présenter 0 volt sur la résistance associée à chaque led pour que celle-ci soit allumée, on aura donc au pire deux combinaisons à tester de ce fait; celle définie et son complément bit à bit.

Essais de validation et corrections

Un premier essai de validation échoue, ainsi que son complément bit à bit. Il semble donc y avoir une erreur dans le schéma de cablâge réalisé. Une vérification avec la 3e photo fournie montre en effet que la combinaison d'entrées trouvée pour IC1 est erronée, comme on peut le voir sur le schéma de cablâge qui porte la trace de cette modification.

Avec la bonne combinaison des entrées on trouve finalement que

- la sortie active de IC1 est la pin 16 (pins 3, 4 , 5 et 6 à 0)

- la sortie active de IC2 est la pin 11 (pins 3 et 4 à 0, pins 6 et 7 à 1)

- la sortie active de IC3 est la pin 2 (pins 3 et 4 à 1, pins 6 et 7 à 0)

Au final il s'avère que la bonne combinaison est ECE001

Un clin d'œil à ECE's Revenge?

la photo fournie en cours de compétition.

|