[PCTF 2012] Write-up ECE's Revenge (500pts)

English version on Big-Daddy's blog

Our aerial reconnaissance drones recently sighted <dead link>these new robot prototypes</dead link> but we cannot figure out how to turn them on (INSERT INAPPROPIATE JOKE). Can you help us solve the mystery and get their electrons flowing?

L'épreuve

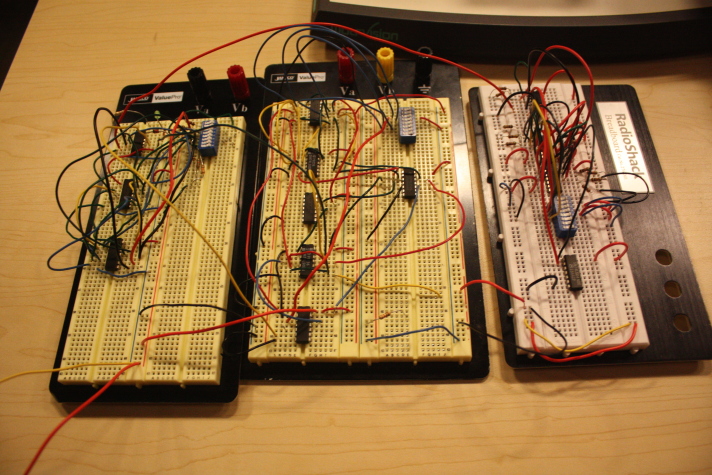

On dispose de photos d'un montage électronique composé de trois plaques d'essai comme on le voit sur la vue générale ci-dessous. Sur chaque plaque il y a un 'DIP switch', assemblage de 8 mini-interrupteurs. Sur l'une des plaques il y a une led (diode électroluminescente). Il faut trouver quelle combinaison des interrupteurs fait s'allumer la led.

Résolution

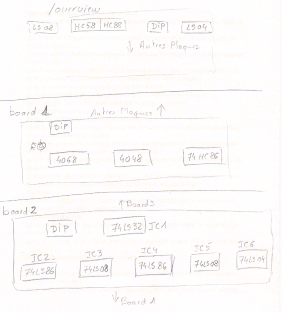

La première étape consiste à repérer et dresser la nomenclature des composants pour chaque plaque d'essai, plaques que l'on repèrera pour la suite de #1 à #3 de gauche à droite sur la vue générale ci-dessus.

Ça nous donne:

Plaque #1:

1x DIP-switch

1x 4048 3-state 8-input multifunction gate

1x 4068 8-input NAND gate

1x 4068 8-input NAND gate

1x 74HC86 Quad 2-input Exclusive Or Gate

1x LED verte

Plaque #2:

1x DIP-switch

1x 74LS04 6 inverseurs

2x 74LS08 Quad 2-input AND Gate

1x 74LS32 Quad 2-input Or Gate

2x 74LS86 Quad 2-input Exclusive Or Gate

Plaque #3:

1x DIP-switch

1x 74LS04 6 inverseurs

1x 74LS08 Quad 2-input AND Gate

1x 74HC58 Dual AND-OR Gate

1x 74HC88 256 bits ROM

Les composants utilisés font partie de séries 74 et 4000 bien connues. Seule la documentation et le brochage du 74HC88 (la ROM) n'a pu être trouvé sur le net.

Les interrupteurs constituant les DIP switch seront nommés S0 à S7 pour chaque plaque.

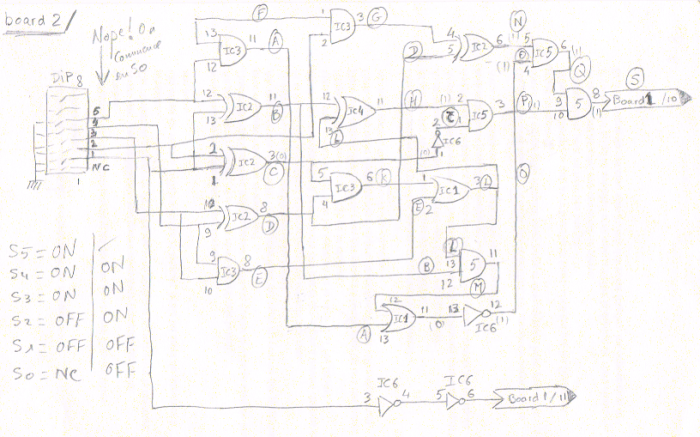

Il faut maintenant reconstituer le schéma électrique de chaque plaque et les interconnexions.

Au bout de quelques heures d'observation méticuleuse des photos fournies (et a peu près au moment ou de nouvelles photos ont été fournies en complément), je dispose des schémas de principe des trois cartes après être passé par une étape intermédiaire consistant à dessiner les liaisons électriques sur le schéma d'implantation, ce qui est plus pratique à relire en cas d'erreur dans le relevé initial du cablâge à partir des photos.

Il reste maintenant à établir le fonctionnement de chaque carte et de l'ensemble.

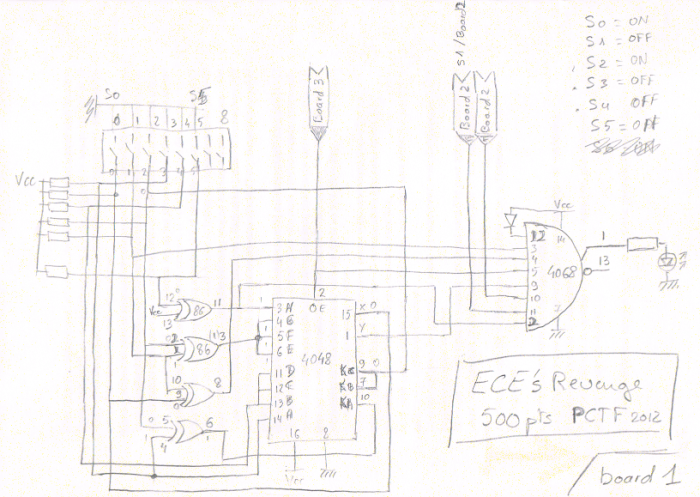

Carte #1

Cette carte reçoit deux signaux en provenance de #2 et un signal de #3. Les deux signaux de #2 attaquent directement les entrées de la porte ET à 8 entrées. Ils doivent donc être tous deux à 1 (état haut - 5 volts) pour avoir un 1 sur la sortie de cette porte et ainsi alimenter la led.

On constate que seul 6 interrupteurs du DIP sont utilisés.

La documentation du 4048 indique que la patte 2 est un Output Enable (OE - activation des sorties) actif à l'état haut. Le signal en provenance de #3 doit donc lui aussi être à 1 pour que la sortie 1 ne soit pas en haute impédance. Ce même signal attaquant aussi le 4068, tout concorde.

La patte 15 est une entrée d'extension, qui doit être mise à 0 si elle n'est pas utilisée. Nous la mettons donc à 0 en fermant l'inter S0. Il en découle un 0 sur la patte 9 du 74HC86 dont la sortie correspondante (patte 8) attaque le 4068. Il faut donc un 1 sur la patte 9 du 74HC86, que l'on obtient avec S1 ouvert. Ceci nous arrange bien puisque S1 attaque aussi une entrée du 4068.

Vient la partie la plus délicate de cette carte. Les pattes 7, 9 et 10 du 4048 définissent le mode de fonctionnement (1 parmis 8). 7 et 9 étant reliées je décide au vu de la table de fonctionnement d'opter pour une configuration en ET logique, juste parce que c'est simple à utiliser. Ce choix va néanmoins s'avérer être le bon.

Il en découle le besoin d'un 0 sur 7 et 9 donc S2=ON et d'avoir un 1 sur toutes les entrées. Ça tombe bien car la patte 3 du 4048 est aussi reliée à une entrée du 4068 et doit donc être à 1. Il suffit pour cela de positionner un 0 sur la patte 12 du 74HC86 en fermant S5.

Pour le reste, S2 fixe un 0 sur la patte 2 du 74HC86, ce qui permet d'avoir un 1 en sortie vu que l'autre entrée du XOR à été mise à 1 par S1. De plus ça tombe bien ici aussi puisqu'on obtient ainsi le 1 nécessaire sur les entrées 4, 5 et 6 du 4048.

Revenons à la 3e ligne de configuration du 4048; la patte 10 qui doit être à 1 pour la config en ET. Le switch S2 ayant fixé à 0 la patte 5 du 74HC86, la patte 4 de ce dernier doit être à 1 pour avoir un 1 en sortie (patte6) et ainsi avoir le 1 requis sur la 10 du 4048. Le switch S3 à OFF permet d'avoir le 1 souhaité sur la 4 du 74HC86 ainsi que sur l'entrée 14 du 4048.

Il nous manque encore 3 entrées du 4048 (pattes 11, 12 et 13) à fixer à 1, ce qui correspond à laisser S4 ouvert.

Voilà pour cette carte.

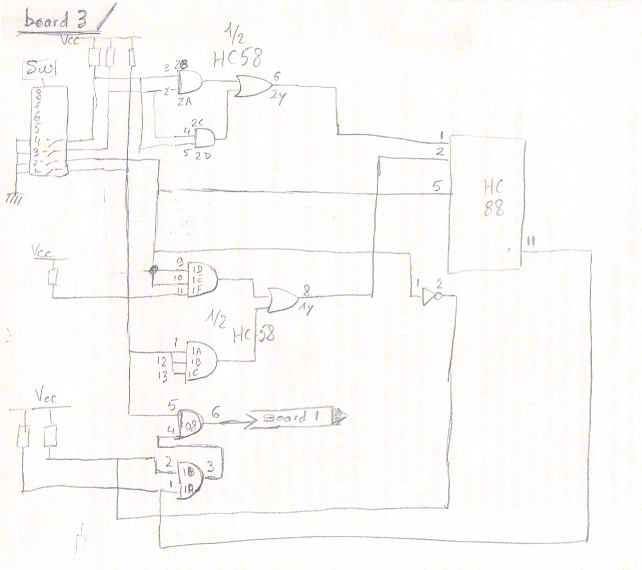

Carte #3

On constate que seul 4 interrupteurs sont utilisés.

On voit que pour avoir un 1 sur la sortie de la carte il faut avoir un 1 sur la patte 5 du 74LS08 ce qui impose S0 à OFF. De ce fait on impose un 1 sur les pattes 1, 12 et 13 du 74HC58 et de là un 1 sur la 2 du 74HC88 indépendament de la valeur des entrées 9,10 et 11 du ET en amont de l'autre entrée du OR intermédiaire. Ainsi S1 reste actuellement positionnable comme on veut, sans effet sur la sortie 8 du 74HC58.

Revenons à la sortie de la carte. Le ET final (74HC08) doit avoir un 1 sur sa patte 4 ce qui implique un 1 sur les pattes 1 et 2 du ET en amont, donc S1 = ON.

En absence de doc sur le 74HC88 je ne peux savoir si la patte 11 est une sortie ou une entrée. Si c'est une entrée elle est mise à 1 par la résistance de pull-up et nous n'avons aucun contrôle dessus. La condition sur la patte 4 du 74HC08 est dans ce cas remplie. Si c'est une sortie elle dépend de l'état des autres pattes. Celles que nous avons détaillé jusqu'ici ne nous laissent pas de choix de configuration qui permettrait de pouvoir agir sur cette sortie.

Voyons donc ce qui nous reste; l'autre moitié du 74HC58 et les switches S2 et S3.

On constate que si S2 ET S3 sont ouverts on à un 1 en 6 du 74HC58. Dans les autres cas on à un 0. Nous avons là un moyen d'action sur la ROM, deux possibilités à tester.

Carte #2

Le schéma montre qu'un des signaux de sortie est relié directement à S1 par l'intermédiaire de deux inverseurs. S1 doit donc être OFF pour avoir un 1 en sortie.

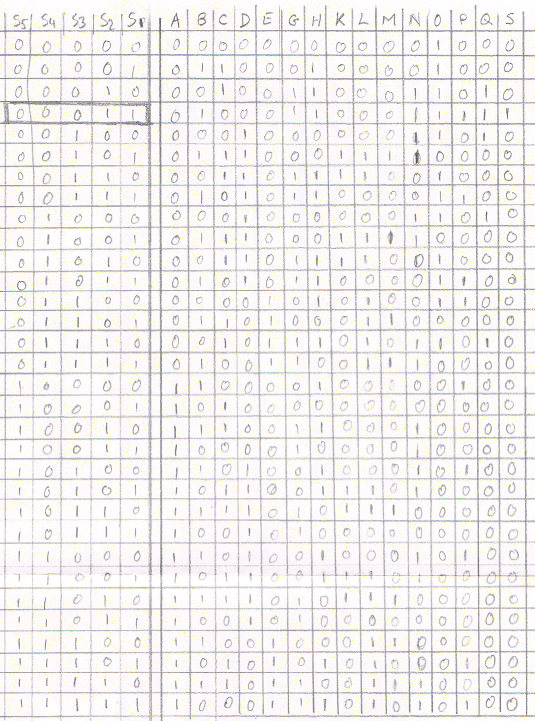

Pour la deuxième sortie il y a un peu plus de monde. À défaut de connaître un logiciel adapté permettant de saisir le schéma et d'obtenir les équations, je nomme les équipotentielles (majuscules entourées) et dresse la table de vérité pour chacune. Comme qui dirait à l'ancienne, quoi. ;-)

Le résultat nous montre que seule une combinaison produit un 1 sur la sortie S. Et cette combinaison requiert comme pour l'autre signal sortant d'avoir S1 à OFF. Tout va bien.

Essais de validation et corrections

On peut maintenant tenter de valider avec seulement 2 combinaisons au total à tester pour la carte #3, l'état des switches des deux autres cartes étant quand à lui entièrement défini. Et là c'est le moment d'angoisse, aucune des deux ne valide.

Après m'être fait confirmer sur le chan IRC officiel que les 1 dans l'interface de validation correspondent bien à un switch fermé, l'explication la plus probable est l'erreur dans le relevé des schémas, ce qui m'amène rapidement à remettre en cause le décalage dans les switchs utilisés sur la carte #2 comme en témoigne le schéma ci-dessus que je n'ai pas corrigé, et à décaler tout d'un cran, S1 devenant S0.

Je tente ainsi la combinaison:

carte #1 10100100 (S0 à S7)

carte #2 00111000

carte #3 01000000

Congratulations! The key is: 1_pr3f3r_p0tat0_ch1p5

It's all done! :-)

|